Neoverse’s Expanding Footprint and the Power-Efficiency Imperative

With Neoverse deployments now approaching roughly 50% of all compute shipped into top hyperscalers in 2025 (representing more than a billion Arm cores) and with nation-scale AI campuses such as the Stargate project already anchored on Arm compute, the addition of NVLink Fusion becomes a pivotal extension of the Neoverse roadmap. Partners can now connect custom Arm CPUs to their preferred NVIDIA accelerators across a coherent, high-bandwidth, rack-scale fabric.

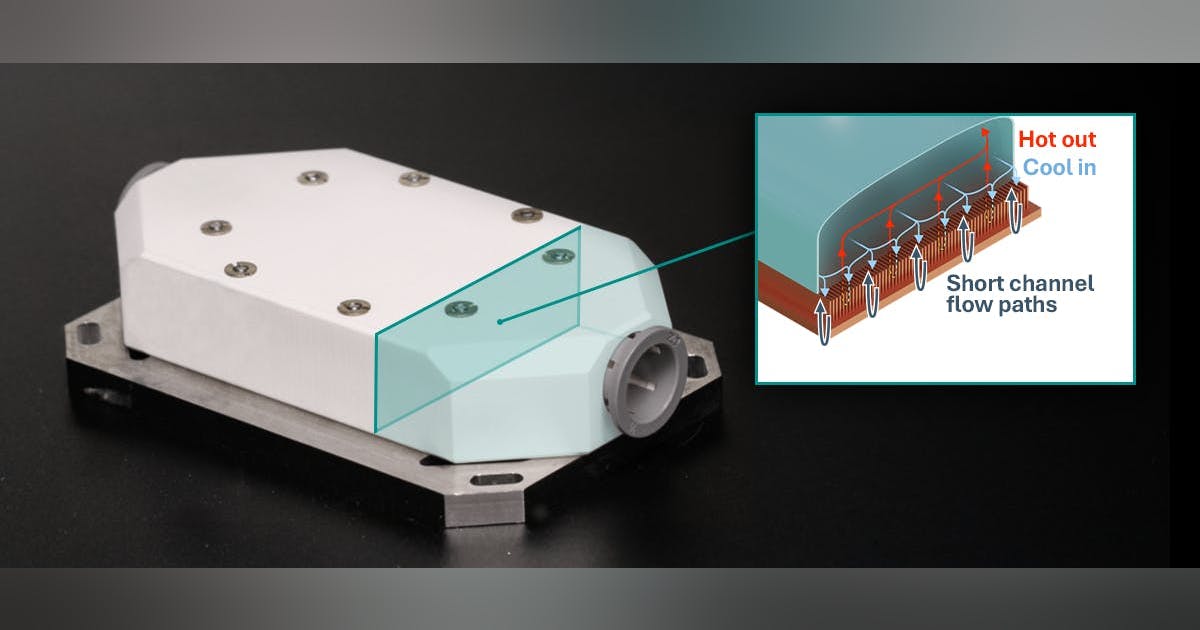

Arm characterized the shift as a generational inflection point in data-center architecture, noting that “power—not FLOPs—is the bottleneck,” and that future design priorities hinge on maximizing “intelligence per watt.”

Ian Buck, vice president and general manager of accelerated computing at NVIDIA, underscored the practical impact:

“Folks building their own Arm CPU, or using an Arm IP, can actually have access to NVLink Fusion—be able to connect that Arm CPU to an NVIDIA GPU or to the rest of the NVLink ecosystem—and that’s happening at the racks and scale-up infrastructure.”

Despite the expanded design flexibility, this is not being positioned as an open interconnect ecosystem. NVIDIA continues to control the NVLink Fusion fabric, and all connections ultimately run through NVIDIA’s architecture.

For data-center planners, the SC25 announcement translates into several concrete implications:

1. NVIDIA “Grace-style” Racks Without Buying Grace

With NVLink Fusion now baked into Neoverse, hyperscalers and sovereign operators can design their own Arm-based control-plane or pre-processing CPUs that attach coherently to NVIDIA GPU domains—such as NVL72 racks or HGX B200/B300 systems—without relying on Grace CPUs.

A rack-level architecture might now resemble:

-

Custom Neoverse SoC for ingest, orchestration, agent logic, and pre/post-processing

-

NVLink Fusion fabric

-

Blackwell GPU islands and/or NVLink-attached custom accelerators (Marvell, MediaTek, others)

This decouples CPU choice from NVIDIA’s GPU roadmap while retaining the full NVLink fabric. In practice, it also opens pathways for operators to slot in lower-cost or workload-specific accelerators for tasks that don’t require the full capabilities of Grace-Blackwell GPU complexes.

CHI C2C—an extension of Arm’s AMBA CHI protocol—underpins this flexibility by enabling coherent and secure communication across chiplets and multi-chip configurations.

2. Rack-Scale Coherence as a Standard Feature

Because NVLink Fusion is coherent end-to-end and integrates directly with CHI C2C, CPU, GPU, and accelerator memory can now operate as a unified pool at rack scale. This generalizes the Grace-Hopper and Grace-Blackwell architecture to any Neoverse implementer.

The design strongly favors large-scale training environments that use heavy tensor or model parallelism within a single NVLink domain. CPUs and on-rack accelerators can now handle streaming, sharding, and I/O without routing traffic through PCIe or NICs for every exchange, reducing latency and smoothing utilization across the rack.

For facility planners, NVLink domains—NVL72 blocks, HGX nodes, and their successors—remain the fundamental unit of “inside-the-rack” scale-up. What changes now is the range of Arm CPU options that can live inside those domains, enabling more customized and power-efficient AI rack designs.

What Comes Next for Neoverse + NVLink Fusion

Neoverse licensees will now need to publicly signal their adoption plans for NVLink Fusion. The industry will be watching for AWS, Google, Microsoft, Oracle, Meta, national labs, and sovereign cloud programs to reference NVLink-enabled Arm CPUs in upcoming roadmaps, procurement cycles, or RFPs. Arm already has meaningful traction inside hyperscale data centers and emerging AI-factory designs; the open question is whether NVLink Fusion represents a step-change, or simply the next stage of an expected evolution.

Pricing also remains an unknown. Tight licensing terms could limit NVLink Fusion to the largest hyperscalers and sovereign operators. More permissive terms could enable second-tier cloud providers and colocation platforms to adopt off-the-shelf Neoverse+NVLink CPUs as part of standardized AI-factory rack designs.

Another complexity is NVIDIA’s own roadmap. The forthcoming NVIDIA Vera Superchips will use custom Arm cores rather than Neoverse V2, even as Neoverse V2 gains native NVLink Fusion support. If this pattern continues, NVIDIA could find itself both relying on Neoverse and competing with Neoverse inside the same coherent fabric. While this duality may initially appear confusing, it could accelerate the shift toward solution-specific CPU/GPU combinations and encourage operators to diversify CPU choices within NVLink domains.